Intel Corporation

EP20K300EFC672-2X

EP20K300EFC672-2X ECAD Model

EP20K300EFC672-2X Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | No | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 1.8 V | |

| Propagation Delay | 2.29 ns | |

| Number of Inputs | 400 | |

| Number of Outputs | 400 | |

| Number of Logic Cells | 11520 | |

| Number of Dedicated Inputs | 4 | |

| Number of I/O Lines | 408 | |

| Programmable Logic Type | LOADABLE PLD | |

| Temperature Grade | OTHER | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 4 DEDICATED INPUTS, 408 I/O | |

| Clock Frequency-Max | 160 MHz | |

| Output Function | MACROCELL | |

| Power Supplies | 1.8,1.8/3.3 V | |

| Supply Voltage-Max | 1.89 V | |

| Supply Voltage-Min | 1.71 V | |

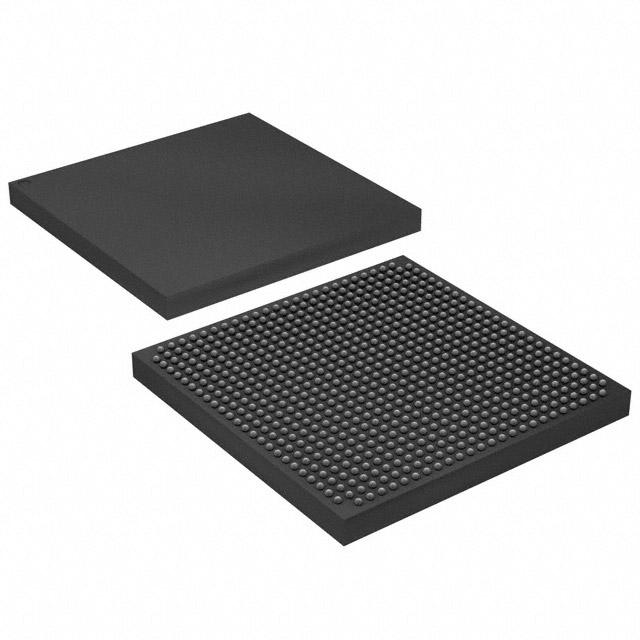

| JESD-30 Code | S-PBGA-B672 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 85 °C | |

| Number of Terminals | 672 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Equivalence Code | BGA672,26X26,40 | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | BALL | |

| Terminal Pitch | 1 mm | |

| Terminal Position | BOTTOM | |

| Width | 27 mm | |

| Length | 27 mm | |

| Seated Height-Max | 3.5 mm | |

| Ihs Manufacturer | INTEL CORP | |

| Package Description | FINE LINE, BGA-672 | |

| Reach Compliance Code | compliant | |

| ECCN Code | 3A991.D | |

| HTS Code | 8542.39.00.01 |

EP20K300EFC672-2X Datasheet Download

EP20K300EFC672-2X Overview

The chip model EP20K300EFC672-2X is an integrated circuit device developed by Altera Corporation, a leading provider of programmable logic solutions. It is a high-performance, low-power FPGA device that can be used for a wide range of applications, including communication systems, robotics, and medical imaging.

The EP20K300EFC672-2X chip model is designed to meet the needs of advanced communication systems. It is capable of providing high-speed data transfer and processing, as well as low power consumption. The chip model also has a high degree of flexibility, allowing for easy customization and upgrades. This makes it an ideal choice for applications that require a high degree of performance and scalability.

The product description and specific design requirements of the EP20K300EFC672-2X chip model are detailed in the Altera Corporation product data sheet. This document outlines the features and capabilities of the chip model, as well as the recommended design practices and precautions. Additionally, it provides a number of case studies and examples of how the chip model can be used in various applications.

In terms of its application in the development and popularization of future intelligent robots, the EP20K300EFC672-2X chip model can be used to provide the necessary processing power and flexibility. However, it is important to note that the use of the chip model requires a certain level of technical expertise. Those who wish to use the chip model effectively must have a strong understanding of FPGA technology and the associated design tools.

Overall, the EP20K300EFC672-2X chip model is a powerful and flexible solution for a wide range of applications. Its original design intention was to meet the needs of advanced communication systems, and its flexibility allows for easy customization and upgrades. Furthermore, the chip model can be used for the development and popularization of future intelligent robots, but requires a certain level of technical expertise.

You May Also Be Interested In

1,317 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||