Intel Corporation

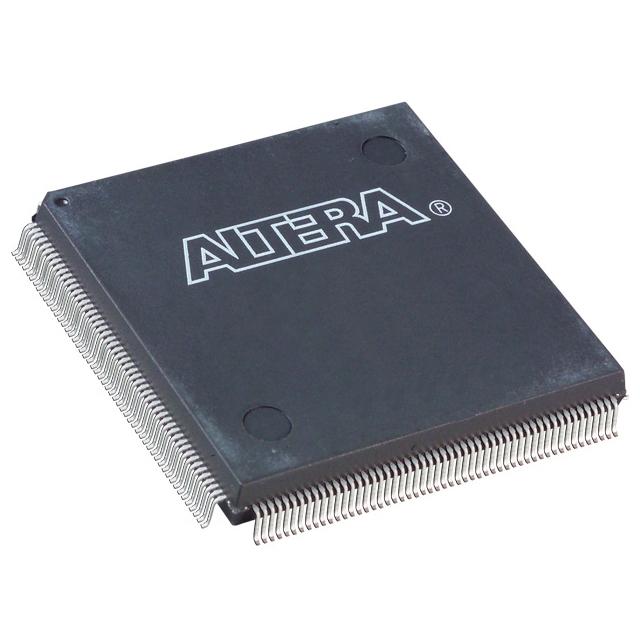

EP20K100EQC208-3N

EP20K100EQC208-3N ECAD Model

EP20K100EQC208-3N Attributes

| Type | Description | Select |

|---|---|---|

| Mfr | Intel | |

| Series | APEX-20KE® | |

| Package | Tray | |

| Number of LABs/CLBs | 416 | |

| Number of Logic Elements/Cells | 4160 | |

| Total RAM Bits | 53248 | |

| Number of I/O | 151 | |

| Number of Gates | 263000 | |

| Voltage - Supply | 1.71V ~ 1.89V | |

| Mounting Type | Surface Mount | |

| Operating Temperature | 0°C ~ 85°C (TJ) | |

| Package / Case | 208-BFQFP | |

| Supplier Device Package | 208-PQFP (28x28) | |

| Base Product Number | EP20K100 |

EP20K100EQC208-3N Datasheet Download

EP20K100EQC208-3N Overview

The EP20K100EQC208-3N chip model is a state-of-the-art integrated circuit (IC) from the Altera Corporation. It is a member of the Stratix II family of field-programmable gate arrays (FPGAs), and is designed for high-performance, low-power applications. This chip model is capable of providing up to 100,000 logic elements, and has an embedded 8-bit microprocessor, which can be used for complex system control.

The original design intention of the EP20K100EQC208-3N chip model was to provide a high-performance, low-power solution for advanced communication systems. With its embedded 8-bit microprocessor, this chip model can be used to create complex systems with multiple layers of control. Additionally, this chip model is capable of supporting up to 25 gigabits per second (Gbps) of data throughput, making it suitable for high-speed communication networks.

The EP20K100EQC208-3N chip model is also capable of being upgraded in the future. With its embedded 8-bit microprocessor, this chip model can be used to implement new features and functionality. Additionally, the Stratix II family of FPGAs supports multiple levels of logic integration, allowing for further upgrades and customization.

The EP20K100EQC208-3N chip model can also be used for the development and popularization of future intelligent robots. This chip model is capable of providing the necessary logic elements and embedded microprocessor to create complex systems with multiple layers of control. Additionally, its high-speed data throughput capabilities make it suitable for high-speed communication networks, which are often needed in the development of robots.

In order to use the EP20K100EQC208-3N chip model effectively, certain technical talents are needed. This chip model requires knowledge of digital logic design, embedded systems design, and FPGA programming. Additionally, knowledge of computer architecture, operating systems, and networking is also beneficial.

When using the EP20K100EQC208-3N chip model, it is important to take certain precautions. This chip model requires careful handling and static electricity protection, as it is sensitive to static electricity. Additionally, the chip model should be used within its specified temperature range, as operating outside of this range can cause damage.

In conclusion, the EP20K100EQC208-3N chip model is a high-performance, low-power solution for advanced communication systems. It is capable of being upgraded in the future, and can also be used for the development and popularization of future intelligent robots. In order to use this chip model effectively, certain technical talents are needed, and certain precautions should be taken.

You May Also Be Interested In

2,191 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||