Intel Corporation

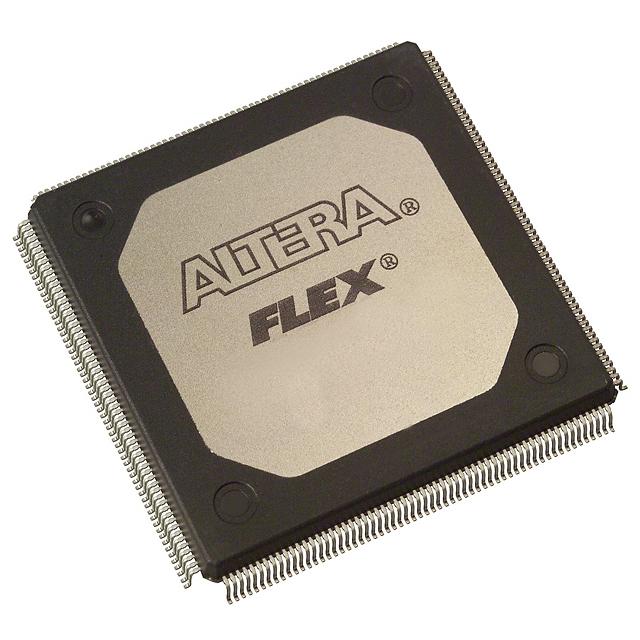

EPF10K70RC240-2N

EPF10K70RC240-2N ECAD Model

EPF10K70RC240-2N Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | Yes | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 5 V | |

| Propagation Delay | 400 ps | |

| Number of Inputs | 189 | |

| Number of Outputs | 189 | |

| Number of Logic Cells | 3744 | |

| Number of Dedicated Inputs | 4 | |

| Number of I/O Lines | 189 | |

| Programmable Logic Type | LOADABLE PLD | |

| Temperature Grade | COMMERCIAL | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 4 DEDICATED INPUTS, 189 I/O | |

| Output Function | REGISTERED | |

| Power Supplies | 3.3/5 V | |

| Supply Voltage-Max | 5.25 V | |

| Supply Voltage-Min | 4.75 V | |

| JESD-30 Code | S-PQFP-G240 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e3 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 70 °C | |

| Number of Terminals | 240 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | HFQFP | |

| Package Equivalence Code | HQFP240,1.37SQ,20 | |

| Package Shape | SQUARE | |

| Package Style | FLATPACK, HEAT SINK/SLUG, FINE PITCH | |

| Surface Mount | YES | |

| Terminal Finish | MATTE TIN | |

| Terminal Form | GULL WING | |

| Terminal Pitch | 500 µm | |

| Terminal Position | QUAD | |

| Width | 32 mm | |

| Length | 32 mm | |

| Seated Height-Max | 4.1 mm | |

| Ihs Manufacturer | INTEL CORP | |

| Package Description | HFQFP, HQFP240,1.37SQ,20 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EPF10K70RC240-2N Datasheet Download

EPF10K70RC240-2N Overview

The EPF10K70RC240-2N chip model is a high-performance chip designed for digital signal processing, embedded processing, and image processing. It is widely used in various industries, such as consumer electronics, medical, military, and aerospace. This chip is capable of handling complex tasks with its powerful processing capabilities and can be used to develop and popularize future intelligent robots.

The EPF10K70RC240-2N chip model is based on a field-programmable gate array (FPGA) architecture and requires the use of HDL language for design implementation. The chip model has multiple features, such as a high-speed clock, high-speed memory, and I/O ports. The chip also features a low-power design, making it suitable for low-power applications. In addition, it has an advanced reconfigurable logic block, which allows for flexible and efficient design implementation.

The EPF10K70RC240-2N chip model is an ideal choice for developers looking for a high-performance chip for their projects. It is also suitable for applications that require high-speed data processing. Its advanced features enable developers to create complex designs with ease.

In order to use the EPF10K70RC240-2N chip model effectively, certain technical skills are required. First, developers should have a good understanding of HDL language and be familiar with the FPGA architecture. They should also have knowledge of the chip model's features, such as the clock speed, memory, and I/O ports. Furthermore, developers should have a good understanding of the chip's reconfigurable logic block and its associated design implementation.

Case studies and precautions should also be taken into consideration when using the EPF10K70RC240-2N chip model. Developers should be familiar with the chip model's limitations to ensure that their designs are optimized for the chip's capabilities. Additionally, developers should also be aware of the chip's power consumption, as this can affect the performance of the design.

The EPF10K70RC240-2N chip model is a powerful and versatile chip that can be used to develop and popularize future intelligent robots. With its powerful processing capabilities and advanced features, the chip model can be used to create complex designs with ease. However, developers should have a good understanding of the chip model's features and limitations in order to use the chip model effectively.

You May Also Be Interested In

3,494 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||