Intel Corporation

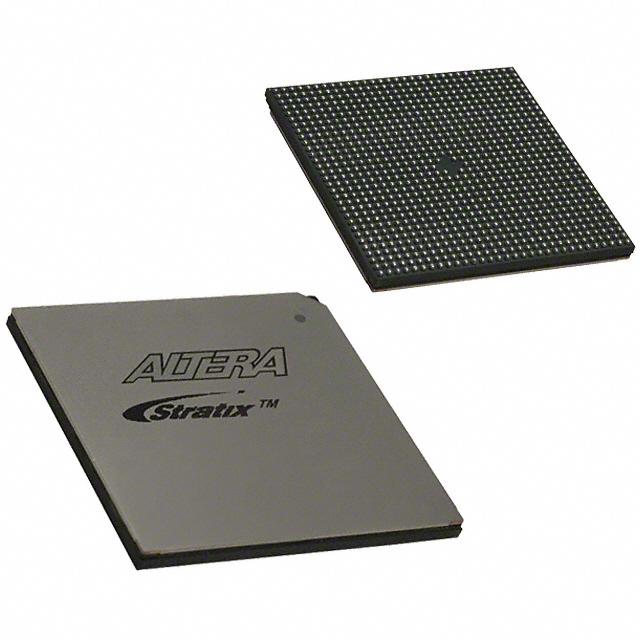

EP1S80B956C6AB

EP1S80B956C6AB ECAD Model

EP1S80B956C6AB Attributes

| Type | Description | Select |

|---|

EP1S80B956C6AB Overview

The chip model EP1S80B956C6AB is a high-performance, high-density FPGA (Field Programmable Gate Array) designed by Altera. It is suitable for high-performance digital signal processing, embedded processing, image processing, and other applications. It can be used to implement complex logic functions and is suitable for applications that require high performance and flexibility. As a result, it is widely used in various fields such as aerospace, medical, automotive, and industrial automation.

The chip model EP1S80B956C6AB is based on the Altera Stratix IV architecture and has a total of 8,096 logic elements, 4,256 embedded memory blocks, and 4,096 DSP blocks. It has a high-speed transceiver with a data rate of up to 10.3125 Gbps. It also has a low-power design feature, which can reduce power consumption by up to 50%. In addition, the chip model EP1S80B956C6AB has a built-in high-speed clock management circuit, which can provide a maximum clock frequency of up to 400 MHz.

The chip model EP1S80B956C6AB requires the use of HDL (Hardware Description Language) to design and implement the logic functions. HDL is a type of programming language that is used to describe the behavior of digital circuits. It is used to create a design description that can be used to synthesize into a physical circuit. The HDL language used for the chip model EP1S80B956C6AB is Verilog, a hardware description language used to design and simulate digital circuits.

When using the chip model EP1S80B956C6AB, it is important to consider the design requirements and product specifications. The chip model EP1S80B956C6AB can be used for a variety of applications, such as digital signal processing, embedded processing, and image processing. It is important to understand the design requirements of the chip model EP1S80B956C6AB and the product specifications before starting the design process. It is also important to consider the power consumption and the clock frequency of the chip model EP1S80B956C6AB.

The chip model EP1S80B956C6AB can be used in the development and popularization of future intelligent robots. It can be used to implement complex logic functions and its low-power design feature can reduce power consumption. In addition, its high-speed transceiver and high-speed clock management circuit can provide a maximum clock frequency of up to 400 MHz. To effectively use the chip model EP1S80B956C6AB, it is important to have a good understanding of the HDL language and the design requirements of the chip model. Technical talents such as software engineers, hardware engineers, and embedded system engineers are needed to effectively use the chip model EP1S80B956C6AB.

You May Also Be Interested In

2,524 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||