AMD Xilinx

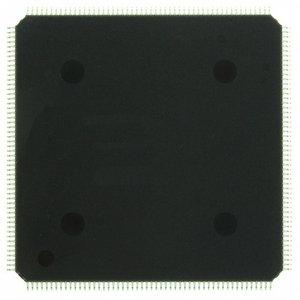

XC2S50E-7PQG208C

XC2S50E-7PQG208C ECAD Model

XC2S50E-7PQG208C Attributes

| Type | Description | Select |

|---|---|---|

| Pbfree Code | Yes | |

| Rohs Code | Yes | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 1.8 V | |

| Number of Inputs | 182 | |

| Number of Outputs | 182 | |

| Number of Logic Cells | 1728 | |

| Number of Equivalent Gates | 23000 | |

| Number of CLBs | 384 | |

| Combinatorial Delay of a CLB-Max | 420 ps | |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | |

| Temperature Grade | OTHER | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 384 CLBS, 23000 GATES | |

| Additional Feature | MAXIMUM USABLE GATES = 50000 | |

| Clock Frequency-Max | 400 MHz | |

| Power Supplies | 1.2/3.6,1.8 V | |

| Supply Voltage-Max | 1.89 V | |

| Supply Voltage-Min | 1.71 V | |

| JESD-30 Code | S-PQFP-G208 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e3 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 85 °C | |

| Peak Reflow Temperature (Cel) | 245 | |

| Time@Peak Reflow Temperature-Max (s) | 30 | |

| Number of Terminals | 208 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | FQFP | |

| Package Equivalence Code | QFP208,1.2SQ,20 | |

| Package Shape | SQUARE | |

| Package Style | FLATPACK, FINE PITCH | |

| Surface Mount | YES | |

| Terminal Finish | Matte Tin (Sn) | |

| Terminal Form | GULL WING | |

| Terminal Pitch | 500 µm | |

| Terminal Position | QUAD | |

| Width | 28 mm | |

| Length | 28 mm | |

| Seated Height-Max | 4.1 mm | |

| Ihs Manufacturer | XILINX INC | |

| Part Package Code | QFP | |

| Package Description | LEAD FREE, PLASTIC, QFP-208 | |

| Pin Count | 208 | |

| Reach Compliance Code | unknown | |

| ECCN Code | EAR99 | |

| HTS Code | 8542.39.00.01 |

XC2S50E-7PQG208C Datasheet Download

XC2S50E-7PQG208C Overview

The XC2S50E-7PQG208C chip model is a great choice for high-performance digital signal processing, embedded processing, and image processing. It is designed to be used with HDL language, which provides a great deal of flexibility and control over the development process. The chip model has several advantages that make it ideal for these applications.

First, the XC2S50E-7PQG208C chip model is highly reliable and efficient. It is designed with a low power consumption and has a long life cycle, making it a great choice for applications that require frequent use. Additionally, it offers high-speed processing and a wide range of features that allow for more complex tasks.

Second, the XC2S50E-7PQG208C chip model is extremely cost-effective. It is designed to be low-cost and requires minimal resources to operate, making it a great choice for applications that require a high level of performance but don’t have a large budget. Furthermore, the chip model is easy to use, making it accessible to developers of all levels.

Given the advantages of the XC2S50E-7PQG208C chip model, it is expected that demand for this model will continue to increase in the future. As the need for high-performance digital signal processing, embedded processing, and image processing grows, the XC2S50E-7PQG208C chip model is likely to become an increasingly popular choice.

The XC2S50E-7PQG208C chip model can be applied to the development and popularization of future intelligent robots, as it offers the necessary performance and features required for complex robotic tasks. However, the effective use of this chip model requires certain technical talents, such as knowledge of HDL language and familiarity with the chip model’s features and capabilities. Additionally, developers must be able to use the chip model to design algorithms and systems that are suitable for robotic applications.

You May Also Be Interested In

2,293 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||