Microchip Technology Inc

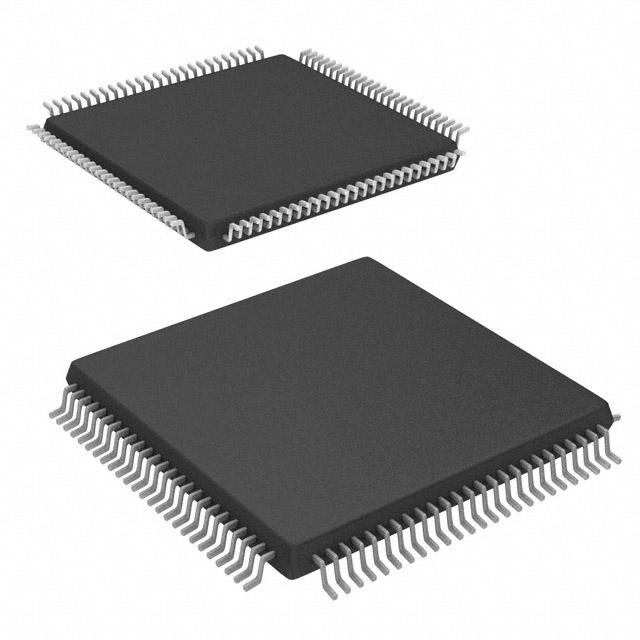

A3PN125-2VQ100I

A3PN125-2VQ100I ECAD Model

A3PN125-2VQ100I Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | No | |

| Part Life Cycle Code | Transferred | |

| Supply Voltage-Nom | 1.5 V | |

| Number of Equivalent Gates | 125000 | |

| Number of CLBs | 3072 | |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | |

| Temperature Grade | INDUSTRIAL | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 3072 CLBS, 125000 GATES | |

| Supply Voltage-Max | 1.575 V | |

| Supply Voltage-Min | 1.425 V | |

| JESD-30 Code | S-PQFP-G100 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 85 °C | |

| Operating Temperature-Min | -40 °C | |

| Number of Terminals | 100 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | TFQFP | |

| Package Shape | SQUARE | |

| Package Style | FLATPACK, THIN PROFILE, FINE PITCH | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | GULL WING | |

| Terminal Pitch | 500 µm | |

| Terminal Position | QUAD | |

| Width | 14 mm | |

| Length | 14 mm | |

| Seated Height-Max | 1.2 mm | |

| Ihs Manufacturer | MICROSEMI CORP | |

| Package Description | TFQFP, | |

| Reach Compliance Code | unknown | |

| HTS Code | 8542.39.00.01 |

A3PN125-2VQ100I Datasheet Download

A3PN125-2VQ100I Overview

The A3PN125-2VQ100I is a Field Programmable Gate Array (FPGA) chip designed by Altera Corporation. It is a member of the Stratix III family of devices, and is based on the 90 nm process technology. This chip has a total of 125,000 logic elements, and offers up to 1.2 million system gates. It has a total of 1,024 18-Kbit block RAMs, and has a total power consumption of up to 10.5 W.

The A3PN125-2VQ100I is suitable for applications requiring high performance and low power consumption. It is ideal for applications that require high data throughput, such as high-speed networking, video processing, wireless communications and medical imaging. It is also suitable for applications that require low latency and high system integration, such as automotive, industrial and military applications.

The A3PN125-2VQ100I supports up to 8,192 user-defined I/O pins, and has on-chip features such as phase-locked loops, high-speed transceivers, clock management, and embedded memory. It also supports various I/O standards, including LVDS, LVPECL, SSTL, and HSTL. Additionally, it supports various board-level features such as power management, thermal management, and system monitoring.

In conclusion, the A3PN125-2VQ100I is a powerful and efficient FPGA chip designed for applications requiring high performance and low power consumption. It is suitable for a wide range of applications, including high-speed networking, video processing, automotive, industrial and military applications.

You May Also Be Interested In

1,714 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| 1+ | $13.3516 | $13.3516 |

| 10+ | $13.2081 | $132.0807 |

| 100+ | $12.4902 | $1,249.0242 |

| 1000+ | $11.7724 | $5,886.2060 |

| 10000+ | $10.7675 | $10,767.4500 |

| The price is for reference only, please refer to the actual quotation! | ||