Intel Corporation

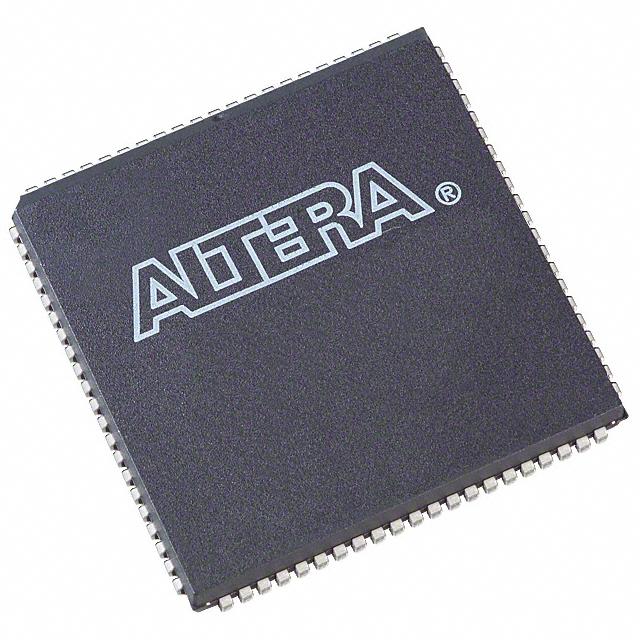

EPM7064SLC84-10

EPM7064SLC84-10 ECAD Model

EPM7064SLC84-10 Attributes

| Type | Description | Select |

|---|---|---|

| Mfr | Intel | |

| Series | MAX® 7000S | |

| Package | Tube | |

| Programmable Type | In System Programmable | |

| Delay Time tpd(1) Max | 10 ns | |

| Voltage Supply - Internal | 4.75V ~ 5.25V | |

| Number of Logic Elements/Blocks | 4 | |

| Number of Macrocells | 64 | |

| Number of Gates | 1250 | |

| Number of I/O | 68 | |

| Operating Temperature | 0°C ~ 70°C (TA) | |

| Mounting Type | Surface Mount | |

| Package / Case | 84-LCC (J-Lead) | |

| Supplier Device Package | 84-PLCC (29.31x29.31) | |

| Base Product Number | EPM7064 |

EPM7064SLC84-10 Datasheet Download

EPM7064SLC84-10 Overview

The EPM7064SLC84-10 is an Altera CPLD (Complex Programmable Logic Device) chip model. It is a high-performance, low-cost, low-power device that has been designed for a wide variety of applications.

The chip is housed in a 100-pin TQFP package and has a maximum operating temperature of 0°C to 70°C. It has a total of 64 macrocells, 4K bits of on-chip RAM and 16K bits of user flash memory. It also features an internal oscillator and clock-generator, as well as 4 input/output (I/O) banks. The I/O banks are configured to support up to 64 I/O pins, with up to 16 pins per bank.

The device is suitable for a wide range of applications, including digital signal processing, embedded systems, data acquisition, and control systems. It is also well-suited for use in industrial, automotive, and consumer electronics applications.

The EPM7064SLC84-10 is easy to program and configure, and it supports both JTAG and Active Serial (AS) programming. It is also compatible with Altera’s Quartus II design software and the Nios II embedded processor.

In summary, the EPM7064SLC84-10 is a low-cost, low-power CPLD chip model that is designed for a wide range of applications. It features 64 macrocells, 4K bits of on-chip RAM, 16K bits of user flash memory, 4 I/O banks, and an internal oscillator and clock-generator. It is easy to program and configure, and it is compatible with Altera’s Quartus II design software and the Nios II embedded processor.

You May Also Be Interested In

4,090 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||