Intel Corporation

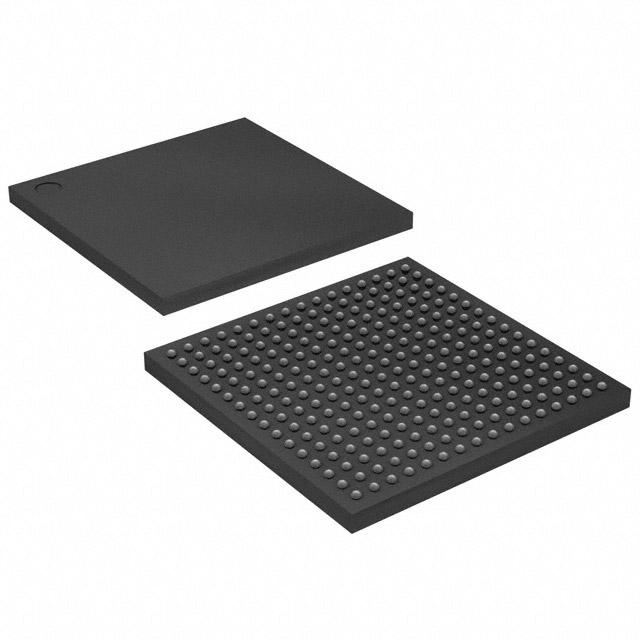

EPF6010AFC256-2

EPF6010AFC256-2 ECAD Model

EPF6010AFC256-2 Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | No | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 3.3 V | |

| Number of Equivalent Gates | 10000 | |

| Number of CLBs | 880 | |

| Combinatorial Delay of a CLB-Max | 2 ns | |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | |

| Temperature Grade | OTHER | |

| Package Shape | SQUARE | |

| Organization | 880 CLBS, 10000 GATES | |

| Clock Frequency-Max | 153 MHz | |

| Supply Voltage-Max | 3.6 V | |

| Supply Voltage-Min | 3 V | |

| JESD-30 Code | S-PBGA-B256 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Operating Temperature-Max | 85 °C | |

| Number of Terminals | 256 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | BALL | |

| Terminal Pitch | 1 mm | |

| Terminal Position | BOTTOM | |

| Width | 17 mm | |

| Length | 17 mm | |

| Ihs Manufacturer | INTEL CORP | |

| Package Description | BGA, | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EPF6010AFC256-2 Datasheet Download

EPF6010AFC256-2 Overview

The chip model EPF6010AFC256-2 is a high-performance integrated circuit with a wide range of applications. It is suitable for high-performance digital signal processing, embedded processing, image processing, and other applications. It is designed to be used with the HDL language, allowing users to develop and implement complex algorithms.

The EPF6010AFC256-2 chip model is designed to provide a wide range of features and performance. It has a 256-bit register file, allowing for complex operations and data storage. The chip also supports a variety of instruction sets, allowing for a wide range of operations to be performed. Additionally, the chip has a high-speed bus architecture, allowing for high-speed data transfer between components.

When using the EPF6010AFC256-2 chip model, it is important to consider the specific design requirements for the application. This includes the number of registers, instruction sets, and bus architecture. Additionally, it is important to ensure that the chip is compatible with the HDL language. It is also important to consider the power consumption of the chip, as this can have an impact on the overall performance of the system.

The EPF6010AFC256-2 chip model can be used in the development and popularization of future intelligent robots. This chip model is ideal for robotics applications, as it provides a wide range of features and performance. Additionally, the chip is compatible with the HDL language, allowing for complex algorithms to be developed and implemented.

In order to use the EPF6010AFC256-2 chip model effectively, it is important to have the right technical skills. This includes knowledge of HDL language, as well as an understanding of the chip's design requirements and power consumption. Additionally, it is important to have a good understanding of robotics and algorithms, as this will allow for the development of more efficient and effective systems.

You May Also Be Interested In

5,602 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||