Intel Corporation

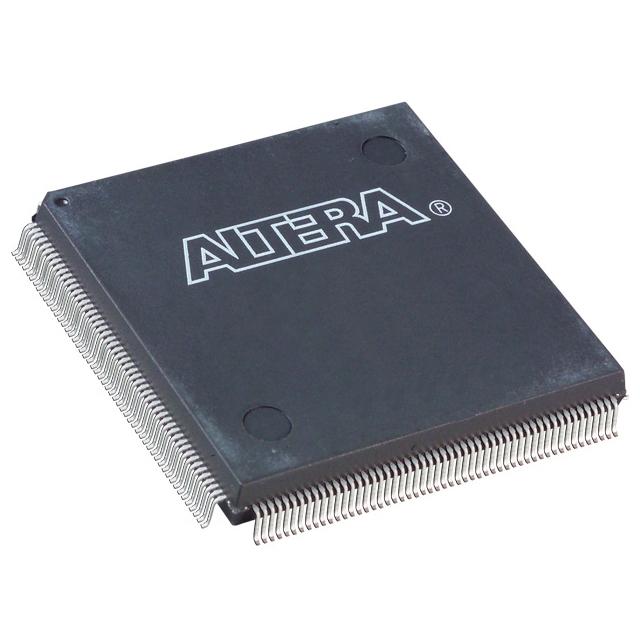

EPF10K50SQC208-3

EPF10K50SQC208-3 ECAD Model

EPF10K50SQC208-3 Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | No | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 2.5 V | |

| Propagation Delay | 500 ps | |

| Number of Inputs | 147 | |

| Number of Outputs | 147 | |

| Number of Logic Cells | 2880 | |

| Number of I/O Lines | 147 | |

| Programmable Logic Type | LOADABLE PLD | |

| Temperature Grade | COMMERCIAL | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 147 I/O | |

| Output Function | MIXED | |

| Power Supplies | 2.5,2.5/3.3 V | |

| Supply Voltage-Max | 2.625 V | |

| Supply Voltage-Min | 2.375 V | |

| JESD-30 Code | S-PQFP-G208 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 70 °C | |

| Number of Terminals | 208 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | FQFP | |

| Package Equivalence Code | QFP208,1.2SQ,20 | |

| Package Shape | SQUARE | |

| Package Style | FLATPACK, FINE PITCH | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | GULL WING | |

| Terminal Pitch | 500 µm | |

| Terminal Position | QUAD | |

| Width | 28 mm | |

| Length | 28 mm | |

| Seated Height-Max | 4.1 mm | |

| Ihs Manufacturer | INTEL CORP | |

| Package Description | FQFP, QFP208,1.2SQ,20 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EPF10K50SQC208-3 Datasheet Download

EPF10K50SQC208-3 Overview

The chip model EPF10K50SQC208-3 is a high-performance, low-power FPGA designed for digital signal processing, embedded processing, and image processing. It is suitable for a variety of applications, such as data acquisition, image processing, communications, and control. Its architecture is optimized for high-speed operation and supports the use of the HDL language for efficient design.

The EPF10K50SQC208-3 is capable of being used in networks and intelligent scenarios to enable the development of fully intelligent systems. It can be used for a variety of tasks, such as machine learning and artificial intelligence, as well as for the development of autonomous systems. This chip also has the potential to be used for the development of autonomous vehicles, drones, and robots.

The product description and design requirements of the EPF10K50SQC208-3 are straightforward. It is an FPGA with a capacity of 10,000 logic elements and 50kbits of embedded RAM. It is designed to operate at a maximum speed of 250 MHz, with a power consumption of 2.8 W. It has two clock domains and two power domains, as well as a variety of I/O options.

In order to ensure the successful implementation of the EPF10K50SQC208-3, it is important to consider the actual case studies and precautions. It is important to consider the timing constraints and the design of the system architecture, as well as the power and clock domains. It is also important to consider the routing and placement of the FPGA, as well as the power and clock distribution. Finally, it is important to consider the testing and verification of the design.

In conclusion, the chip model EPF10K50SQC208-3 is an excellent choice for high-performance digital signal processing, embedded processing, and image processing applications. It is capable of being used in networks and intelligent scenarios to enable the development of fully intelligent systems. It is important to consider the product description and design requirements, as well as actual case studies and precautions, in order to ensure the successful implementation of the EPF10K50SQC208-3.

You May Also Be Interested In

1,891 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| 1+ | $72.8103 | $72.8103 |

| 10+ | $72.0274 | $720.2735 |

| 100+ | $68.1128 | $6,811.2822 |

| 1000+ | $64.1983 | $32,099.1460 |

| 10000+ | $58.7180 | $58,717.9500 |

| The price is for reference only, please refer to the actual quotation! | ||