Intel Corporation

EPF10K100EFC484-3

EPF10K100EFC484-3 ECAD Model

EPF10K100EFC484-3 Attributes

| Type | Description | Select |

|---|---|---|

| Pbfree Code | No | |

| Rohs Code | No | |

| Part Life Cycle Code | Transferred | |

| Supply Voltage-Nom | 2.5 V | |

| Propagation Delay | 700 ps | |

| Number of Inputs | 338 | |

| Number of Outputs | 338 | |

| Number of Logic Cells | 4992 | |

| Number of I/O Lines | 338 | |

| Programmable Logic Type | LOADABLE PLD | |

| Temperature Grade | COMMERCIAL | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 338 I/O | |

| Output Function | MIXED | |

| Power Supplies | 2.5,2.5/3.3 V | |

| Supply Voltage-Max | 2.625 V | |

| Supply Voltage-Min | 2.375 V | |

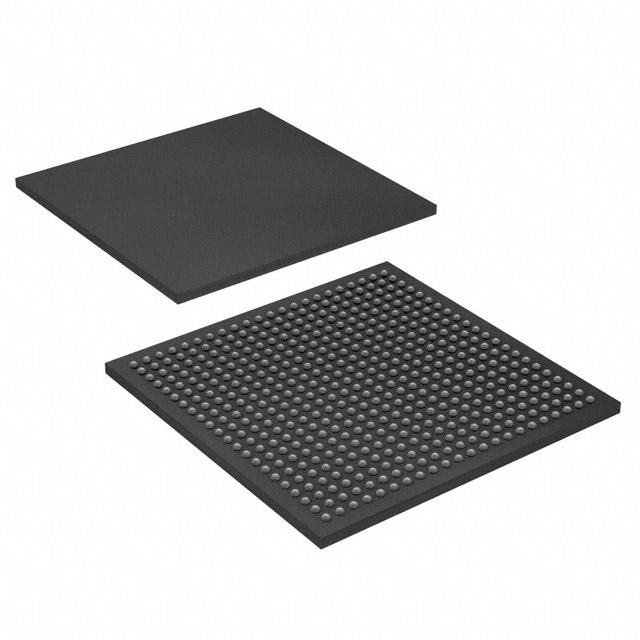

| JESD-30 Code | S-PBGA-B484 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 70 °C | |

| Peak Reflow Temperature (Cel) | 220 | |

| Time@Peak Reflow Temperature-Max (s) | 20 | |

| Number of Terminals | 484 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Equivalence Code | BGA484,22X22,40 | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | BALL | |

| Terminal Pitch | 1 mm | |

| Terminal Position | BOTTOM | |

| Width | 23 mm | |

| Length | 23 mm | |

| Seated Height-Max | 2.1 mm | |

| Ihs Manufacturer | ALTERA CORP | |

| Part Package Code | BGA | |

| Package Description | 23 X 23 MM, 1 MM PITCH, FINE LINE, BGA-484 | |

| Pin Count | 484 | |

| Reach Compliance Code | not_compliant | |

| HTS Code | 8542.39.00.01 | |

| ECCN Code | 3A991.D |

EPF10K100EFC484-3 Overview

The chip model EPF10K100EFC484-3 is a high-performance, low-cost FPGA device that is suitable for a wide range of applications, such as high-performance digital signal processing, embedded processing, and image processing. It is designed to be used with the HDL language, making it a great choice for the development of complex systems. The chip model EPF10K100EFC484-3 offers a number of advantages over traditional processors, such as high speed, low power consumption, and flexibility.

The demand for the EPF10K100EFC484-3 chip model is expected to increase in the future as more industries move towards using FPGA devices for their applications. This is due to the fact that FPGA devices offer a number of advantages over traditional processors, such as high speed, low power consumption, and flexibility. Additionally, FPGA devices are becoming increasingly popular in the development of complex systems, such as autonomous vehicles and robotics.

The EPF10K100EFC484-3 chip model can certainly be applied to the development and popularization of future intelligent robots. The chip model offers a number of advantages over traditional processors, such as high speed, low power consumption, and flexibility. Additionally, it is designed to be used with the HDL language, making it a great choice for the development of complex systems. In order to use the EPF10K100EFC484-3 chip model effectively, technical talents such as engineers, software developers, and designers are needed. These professionals should have a good understanding of the HDL language, as well as experience in the development of complex systems.

You May Also Be Interested In

1,165 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||