Intel Corporation

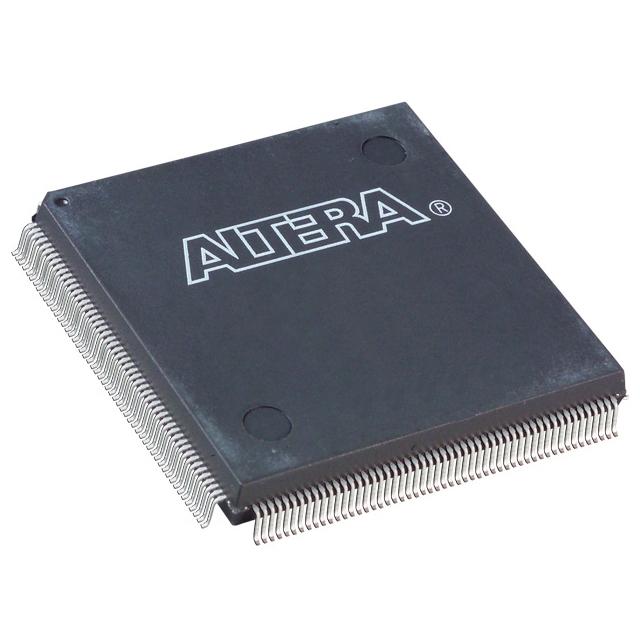

EP20K60EQC208-3N

EP20K60EQC208-3N ECAD Model

EP20K60EQC208-3N Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | Yes | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 1.8 V | |

| Propagation Delay | 3.56 ns | |

| Number of Inputs | 140 | |

| Number of Outputs | 140 | |

| Number of Logic Cells | 2560 | |

| Number of Dedicated Inputs | 4 | |

| Number of I/O Lines | 148 | |

| Programmable Logic Type | LOADABLE PLD | |

| Temperature Grade | OTHER | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 4 DEDICATED INPUTS, 148 I/O | |

| Clock Frequency-Max | 160 MHz | |

| Output Function | MACROCELL | |

| Power Supplies | 1.8,1.8/3.3 V | |

| Supply Voltage-Max | 1.89 V | |

| Supply Voltage-Min | 1.71 V | |

| JESD-30 Code | S-PQFP-G208 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e3 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 85 °C | |

| Number of Terminals | 208 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | FQFP | |

| Package Equivalence Code | QFP208,1.2SQ,20 | |

| Package Shape | SQUARE | |

| Package Style | FLATPACK, FINE PITCH | |

| Surface Mount | YES | |

| Terminal Finish | MATTE TIN | |

| Terminal Form | GULL WING | |

| Terminal Pitch | 500 µm | |

| Terminal Position | QUAD | |

| Width | 28 mm | |

| Length | 28 mm | |

| Seated Height-Max | 4.1 mm | |

| Ihs Manufacturer | INTEL CORP | |

| Package Description | FQFP, QFP208,1.2SQ,20 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EP20K60EQC208-3N Datasheet Download

EP20K60EQC208-3N Overview

The chip model EP20K60EQC208-3N is a high-performance digital signal processing chip that is suitable for embedded processing, image processing and other applications. It is designed to be used with hardware description language (HDL) and is able to meet the needs of high-performance digital signal processing.

In terms of industry trends, the chip model EP20K60EQC208-3N is able to keep up with the development of the industry. As the industry progresses, new technologies may be required in order to ensure that the application environment is up to date. To this end, the chip model EP20K60EQC208-3N is designed to be upgradeable and is capable of being applied to advanced communication systems.

The original design intention of the chip model EP20K60EQC208-3N is to provide a high-performance digital signal processing solution for embedded processing, image processing, and other applications. The chip model is designed to be able to meet the needs of both current and future applications, and can be upgraded when necessary. This allows the chip model to remain up to date and be applicable to advanced communication systems.

Overall, the chip model EP20K60EQC208-3N is a versatile and powerful digital signal processing solution. It is suitable for embedded processing, image processing and other applications, and is designed to be used with HDL language. It is designed to keep up with the industry trends, and is upgradable to ensure that it remains applicable to advanced communication systems.

You May Also Be Interested In

5,105 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||