Intel Corporation

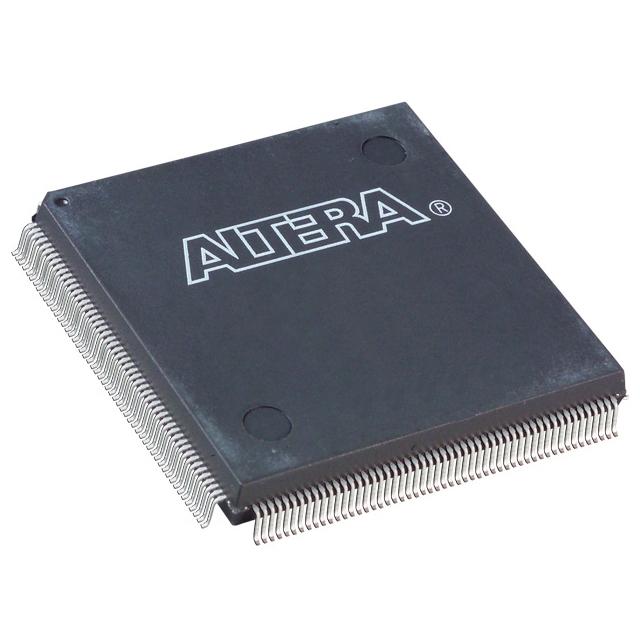

EP20K200EQC208-1

EP20K200EQC208-1 ECAD Model

EP20K200EQC208-1 Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | No | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 1.8 V | |

| Propagation Delay | 1.58 ns | |

| Number of Inputs | 128 | |

| Number of Outputs | 128 | |

| Number of Logic Cells | 8320 | |

| Number of Dedicated Inputs | 4 | |

| Number of I/O Lines | 136 | |

| Programmable Logic Type | LOADABLE PLD | |

| Temperature Grade | OTHER | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 4 DEDICATED INPUTS, 136 I/O | |

| Output Function | MACROCELL | |

| Power Supplies | 1.8,1.8/3.3 V | |

| Supply Voltage-Max | 1.89 V | |

| Supply Voltage-Min | 1.71 V | |

| JESD-30 Code | S-PQFP-G208 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Moisture Sensitivity Level | 3 | |

| Operating Temperature-Max | 85 °C | |

| Number of Terminals | 208 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | FQFP | |

| Package Equivalence Code | QFP208,1.2SQ,20 | |

| Package Shape | SQUARE | |

| Package Style | FLATPACK, FINE PITCH | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | GULL WING | |

| Terminal Pitch | 500 µm | |

| Terminal Position | QUAD | |

| Width | 28 mm | |

| Length | 28 mm | |

| Seated Height-Max | 4.1 mm | |

| Ihs Manufacturer | INTEL CORP | |

| Package Description | FQFP, QFP208,1.2SQ,20 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EP20K200EQC208-1 Datasheet Download

EP20K200EQC208-1 Overview

The chip model EP20K200EQC208-1 is a powerful and reliable programmable logic device (PLD) designed by Altera Corporation. It is a high-speed, low-power, low-cost FPGA device that supports a variety of applications. With its advanced features, the chip model EP20K200EQC208-1 is suitable for a wide range of applications, such as embedded systems, industrial automation, and medical equipment.

The chip model EP20K200EQC208-1 is based on the Stratix II architecture, which provides high-performance, low-power, and low-cost design solutions for a variety of applications. It has a total of 20K logic elements, 200Kbits of RAM, and 8Kbits of distributed RAM. The device also has a variety of I/O options, including LVDS, PCI, and USB. It also supports up to 8 independent clock domains, which makes it ideal for high-performance applications.

The chip model EP20K200EQC208-1 has a number of advantages that make it an ideal choice for a variety of applications. It has a low power consumption, which makes it suitable for battery-powered applications. Its high-speed performance makes it suitable for high-performance applications, while its low-cost design makes it an affordable choice for a variety of applications.

The chip model EP20K200EQC208-1 is expected to be in high demand in the future, as more and more applications require advanced features and technologies. It is already being used in a variety of applications, such as embedded systems, industrial automation, and medical equipment. As new technologies emerge, the chip model EP20K200EQC208-1 will continue to be in demand, as it is capable of supporting the latest technologies.

When designing with the chip model EP20K200EQC208-1, it is important to consider the specific design requirements of the application. For example, it is important to consider the power requirements, the I/O options, and the clock domains. It is also important to consider the size and complexity of the design, as well as the specific features that are required for the application. Additionally, it is important to consider the cost of the design, as well as the cost of the development tools.

In conclusion, the chip model EP20K200EQC208-1 is a powerful and reliable programmable logic device (PLD) designed by Altera Corporation. It is a high-speed, low-power, and low-cost FPGA device that supports a variety of applications. It is expected to be in high demand in the future, as more and more applications require advanced features and technologies. When designing with the chip model EP20K200EQC208-1, it is important to consider the specific design requirements of the application, such as the power requirements, the I/O options, and the clock domains. Additionally, it is important to consider the cost of the design, as well as the cost of the development tools.

You May Also Be Interested In

2,068 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||