Altera Corporation

EP3SE110F1152I2N

EP3SE110F1152I2N ECAD Model

EP3SE110F1152I2N Attributes

| Type | Description | Select |

|---|---|---|

| Pbfree Code | Yes | |

| Rohs Code | Yes | |

| Part Life Cycle Code | Transferred | |

| Number of Inputs | 744 | |

| Number of Outputs | 744 | |

| Number of Logic Cells | 107500 | |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Clock Frequency-Max | 100 MHz | |

| Power Supplies | 1.2/3.3 V | |

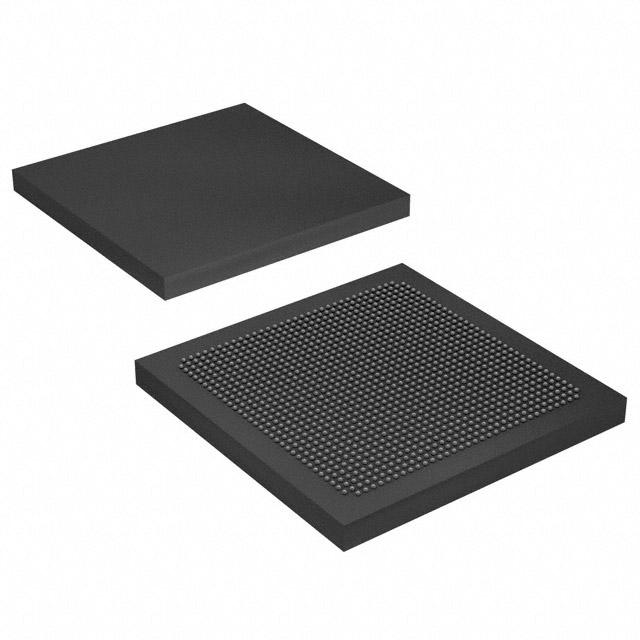

| JESD-30 Code | S-PBGA-B1152 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e1 | |

| Number of Terminals | 1152 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Equivalence Code | BGA1152,34X34,40 | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN SILVER COPPER | |

| Terminal Form | BALL | |

| Terminal Pitch | 1 mm | |

| Terminal Position | BOTTOM | |

| Ihs Manufacturer | ALTERA CORP | |

| Package Description | BGA, BGA1152,34X34,40 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EP3SE110F1152I2N Datasheet Download

EP3SE110F1152I2N Overview

The chip model EP3SE110F1152I2N is a high-performance, low-power FPGA that is suitable for a variety of applications, including digital signal processing, embedded processing, and image processing. This chip model is designed to be programmed using the HDL language, allowing users to customize the design to meet their specific needs.

The EP3SE110F1152I2N chip model offers many advantages, such as low power consumption, high performance, and flexibility. Its low power consumption makes it ideal for applications that require long-term operation, while its high performance allows it to handle complex tasks quickly and efficiently. Moreover, its flexibility allows users to customize their designs to meet their specific requirements.

The EP3SE110F1152I2N chip model is expected to see increasing demand in the future, as more and more applications require the use of FPGAs. In particular, the chip model is expected to be in high demand for applications that require high-speed processing, as well as applications that require low power consumption.

When designing with the EP3SE110F1152I2N chip model, there are certain design requirements that must be met. This includes selecting the correct I/O standards, clock sources, and memory configurations. Additionally, it is important to consider the power and timing constraints of the design, as well as the overall system requirements.

Case studies can be used to illustrate the effectiveness of the EP3SE110F1152I2N chip model. For example, the chip model has been used in a variety of applications, such as high-speed video processing, image processing, and embedded processing. In each of these applications, the chip model was able to provide the desired performance and power consumption.

Finally, it is important to consider certain precautions when using the EP3SE110F1152I2N chip model. This includes ensuring that the design meets the specified power and timing constraints, as well as making sure that the design does not exceed the maximum operating temperature of the chip. Additionally, it is important to ensure that the design is compatible with the selected I/O standards, clock sources, and memory configurations.

Overall, the EP3SE110F1152I2N chip model is an excellent choice for a variety of applications, such as digital signal processing, embedded processing, and image processing. Its low power consumption, high performance, and flexibility make it a great choice for applications that require long-term operation, as well as applications that require high-speed processing. Additionally, it is important to consider the design requirements, case studies, and precautions when using the chip model.

You May Also Be Interested In

2,598 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||