Altera Corporation

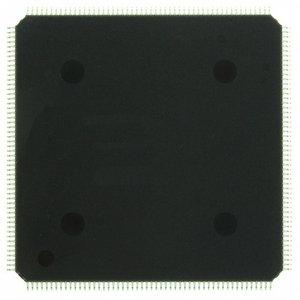

EP20K60EQI208-3

EP20K60EQI208-3 ECAD Model

EP20K60EQI208-3 Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | No | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 2.5 V | |

| Number of Inputs | 140 | |

| Number of Outputs | 140 | |

| Number of Logic Cells | 2560 | |

| Number of Dedicated Inputs | 4 | |

| Number of I/O Lines | 148 | |

| Programmable Logic Type | LOADABLE PLD | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 4 DEDICATED INPUTS, 148 I/O | |

| Output Function | MACROCELL | |

| Power Supplies | 1.8,1.8/3.3 V | |

| Supply Voltage-Max | 2.625 V | |

| Supply Voltage-Min | 2.375 V | |

| JESD-30 Code | S-PQFP-G208 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e3 | |

| Moisture Sensitivity Level | 3 | |

| Peak Reflow Temperature (Cel) | 220 | |

| Number of Terminals | 208 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | FQFP | |

| Package Equivalence Code | QFP208,1.2SQ,20 | |

| Package Shape | SQUARE | |

| Package Style | FLATPACK, FINE PITCH | |

| Surface Mount | YES | |

| Terminal Finish | MATTE TIN | |

| Terminal Form | GULL WING | |

| Terminal Pitch | 500 µm | |

| Terminal Position | QUAD | |

| Width | 28 mm | |

| Length | 28 mm | |

| Seated Height-Max | 4.1 mm | |

| Ihs Manufacturer | ALTERA CORP | |

| Part Package Code | QFP | |

| Package Description | FQFP, QFP208,1.2SQ,20 | |

| Pin Count | 208 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EP20K60EQI208-3 Datasheet Download

EP20K60EQI208-3 Overview

The chip model EP20K60EQI208-3 is a high-performance digital signal processor (DSP) developed by Altera. It is suitable for a wide range of applications such as embedded processing, image processing, and other high-performance digital signal processing. Its design requires the use of the HDL language.

The EP20K60EQI208-3 chip model has several advantages over other models, such as its high performance, low power consumption, and low cost. It is also designed to be compatible with most existing hardware, making it an ideal choice for applications that require high-performance digital signal processing.

The EP20K60EQI208-3 chip model is expected to be in high demand in the near future due to its advantages and its low cost. This chip model is especially suitable for applications that require high-performance digital signal processing and embedded processing, such as those used in medical, aerospace, and automotive industries.

The EP20K60EQI208-3 chip model has specific design requirements that must be met in order to achieve the desired results. The design requires the use of the HDL language, which is a high-level language used to describe the behavior of hardware components. This language is used to design the chip in a way that it can perform the desired tasks.

In order to demonstrate the effectiveness of the EP20K60EQI208-3 chip model, several case studies have been conducted. These case studies have shown that the chip model is able to achieve the desired results in a variety of applications, such as image processing, embedded processing, and other high-performance digital signal processing.

When designing the EP20K60EQI208-3 chip model, it is important to take into consideration the specific design requirements and the actual case studies. It is also important to ensure that the chip model is properly tested before it is put into use, as this will help to ensure that the desired results are achieved.

You May Also Be Interested In

3,720 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||