Altera Corporation

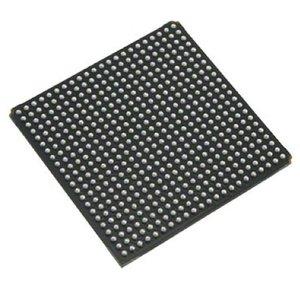

EP20K200EFI484-1

EP20K200EFI484-1 ECAD Model

EP20K200EFI484-1 Attributes

| Type | Description | Select |

|---|---|---|

| Rohs Code | No | |

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 1.8 V | |

| Number of Inputs | 368 | |

| Number of Outputs | 368 | |

| Number of Logic Cells | 8320 | |

| Number of Dedicated Inputs | 4 | |

| Number of I/O Lines | 376 | |

| Programmable Logic Type | LOADABLE PLD | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Organization | 4 DEDICATED INPUTS, 376 I/O | |

| Output Function | MACROCELL | |

| Power Supplies | 1.8,1.8/3.3 V | |

| JESD-30 Code | S-PBGA-B484 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e1 | |

| Moisture Sensitivity Level | 3 | |

| Peak Reflow Temperature (Cel) | 220 | |

| Number of Terminals | 484 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Equivalence Code | BGA484,22X22,40 | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN SILVER COPPER | |

| Terminal Form | BALL | |

| Terminal Pitch | 1 mm | |

| Terminal Position | BOTTOM | |

| Ihs Manufacturer | ALTERA CORP | |

| Package Description | BGA, BGA484,22X22,40 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 | |

| ECCN Code | 3A991.D |

EP20K200EFI484-1 Datasheet Download

EP20K200EFI484-1 Overview

The EP20K200EFI484-1 chip model is a high-performance digital signal processing, embedded processing, and image processing solution. It is designed for applications that require the use of HDL language and is capable of meeting the needs of a variety of industries.

The EP20K200EFI484-1 chip model offers a number of advantages, including its high-speed operation, low power consumption, and wide range of features. As a result, it can be used in a variety of applications, including telecommunications, automotive, industrial automation, medical, and consumer electronics. The chip model also offers a wide range of programming options, making it suitable for a variety of tasks.

The EP20K200EFI484-1 chip model is designed to meet the needs of a variety of industries. It is designed to be compatible with a variety of hardware and software platforms, making it an ideal solution for a variety of applications. It is also designed to be highly reliable and efficient, making it a great choice for high-performance applications.

The design requirements of the EP20K200EFI484-1 chip model are extensive. It requires the use of HDL language, and it is important to understand the language and the design requirements before attempting to use the chip model. In addition, the chip model requires the use of specific tools and software, such as compilers and debuggers. It is also important to understand the specific design requirements of the chip model before attempting to use it.

Case studies and precautions should also be taken into account when designing an application with the EP20K200EFI484-1 chip model. It is important to understand the specific design requirements of the chip model, as well as the specific requirements of the application. Additionally, it is important to understand the specific features and capabilities of the chip model, as well as any potential risks or issues that may arise.

The EP20K200EFI484-1 chip model is a powerful and reliable solution for a variety of applications. It offers a wide range of features and programming options, making it ideal for a variety of tasks. It is designed to be highly reliable and efficient, making it a great choice for high-performance applications. With its wide range of features and programming options, the EP20K200EFI484-1 chip model is expected to continue to be in demand in the future.

You May Also Be Interested In

2,840 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||