Altera Corporation

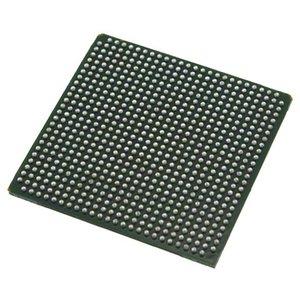

EP1SGX25FF1020C6ES

EP1SGX25FF1020C6ES ECAD Model

EP1SGX25FF1020C6ES Attributes

| Type | Description | Select |

|---|---|---|

| Pbfree Code | No | |

| Rohs Code | No | |

| Part Life Cycle Code | Transferred | |

| Supply Voltage-Nom | 1.5 V | |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | |

| Temperature Grade | OTHER | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Supply Voltage-Max | 1.575 V | |

| Supply Voltage-Min | 1.425 V | |

| JESD-30 Code | S-PBGA-B1020 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Operating Temperature-Max | 85 °C | |

| Number of Terminals | 1020 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | BALL | |

| Terminal Pitch | 1 mm | |

| Terminal Position | BOTTOM | |

| Width | 33 mm | |

| Length | 33 mm | |

| Seated Height-Max | 3.5 mm | |

| Ihs Manufacturer | ALTERA CORP | |

| Part Package Code | BGA | |

| Package Description | BGA, | |

| Pin Count | 1020 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EP1SGX25FF1020C6ES Datasheet Download

EP1SGX25FF1020C6ES Overview

The chip model EP1SGX25FF1020C6ES is a high-performance FPGA chip designed to meet the needs of digital signal processing, embedded processing, and image processing. It is suitable for applications such as high-performance computing, real-time control, and high-speed data processing. It requires the use of HDL language for programming and design.

The product description of the chip model EP1SGX25FF1020C6ES includes its features, such as its high-speed processing capabilities, low power consumption and high integration. It also includes its various I/O interfaces, such as Ethernet, USB, and PCIe. Furthermore, it includes its various development tools, such as the Quartus Prime software, which is used for programming, and the ModelSim software, which is used for simulation.

The specific design requirements of the chip model EP1SGX25FF1020C6ES include the understanding of the FPGA architecture and the ability to use HDL language for programming. It also requires knowledge of the various development tools and their functions. Furthermore, it requires the ability to design and implement digital logic circuits, as well as the ability to debug and troubleshoot the design.

Case studies and precautions to consider when using the chip model EP1SGX25FF1020C6ES include the understanding of the FPGA architecture, the use of the appropriate development tools, the use of the appropriate HDL language, and the use of the appropriate design techniques. Furthermore, it is important to consider the power consumption and timing constraints of the design, as well as the design's scalability and flexibility.

The chip model EP1SGX25FF1020C6ES can be applied to the development and popularization of future intelligent robots, as it is suitable for high-performance computing, real-time control, and high-speed data processing. To use the model effectively, technical talents such as FPGA designers and HDL developers are required. Furthermore, knowledge of the various development tools, the FPGA architecture, and the appropriate design techniques are also necessary.

You May Also Be Interested In

5,181 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||