Altera Corporation

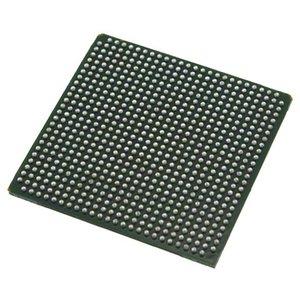

EP1S20F672C7ES

EP1S20F672C7ES ECAD Model

EP1S20F672C7ES Attributes

| Type | Description | Select |

|---|---|---|

| Pbfree Code | No | |

| Rohs Code | No | |

| Part Life Cycle Code | Transferred | |

| Supply Voltage-Nom | 1.5 V | |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | |

| Temperature Grade | OTHER | |

| Package Shape | SQUARE | |

| Technology | CMOS | |

| Supply Voltage-Max | 1.575 V | |

| Supply Voltage-Min | 1.425 V | |

| JESD-30 Code | S-PBGA-B672 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e0 | |

| Operating Temperature-Max | 85 °C | |

| Number of Terminals | 672 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN LEAD | |

| Terminal Form | BALL | |

| Terminal Position | BOTTOM | |

| Ihs Manufacturer | ALTERA CORP | |

| Part Package Code | BGA | |

| Package Description | 35 X 35 MM, 1.27 MM PITCH, BGA-672 | |

| Pin Count | 672 | |

| Reach Compliance Code | compliant | |

| HTS Code | 8542.39.00.01 |

EP1S20F672C7ES Datasheet Download

EP1S20F672C7ES Overview

The chip model EP1S20F672C7ES is a high-performance digital signal processing product developed by Altera Corporation. It is a member of the Stratix series Field Programmable Gate Array (FPGA) family, and is suitable for embedded processing, image processing, and other applications that require high performance. As a member of the Stratix series, the EP1S20F672C7ES chip model offers a wide range of features and capabilities, including a high-speed transceiver, on-chip memory, and high-speed logic.

The EP1S20F672C7ES chip model is designed to be used with the HDL language, which is a hardware description language used to design, simulate, and debug digital circuits. The language allows developers to create complex digital circuits that are optimized for a particular application. The EP1S20F672C7ES chip model can be used to create high-performance digital signal processing applications, as well as embedded processing and image processing applications.

In order to use the EP1S20F672C7ES chip model effectively, developers must have a certain level of technical knowledge and experience. This includes a solid understanding of the HDL language, as well as the ability to design, simulate, and debug digital circuits. Additionally, developers should have a good understanding of the features and capabilities of the chip model, as well as the design requirements and product description.

When it comes to the development and popularization of future intelligent robots, the EP1S20F672C7ES chip model can certainly be applied. With its advanced features and capabilities, the chip model can be used to create powerful and efficient robots that can perform a variety of tasks. However, in order to use the EP1S20F672C7ES chip model effectively, developers must have a certain level of technical knowledge and experience, as well as the ability to design, simulate, and debug digital circuits. Additionally, developers must be familiar with the product description and specific design requirements of the chip model, as well as actual case studies and precautions.

You May Also Be Interested In

2,158 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| 1+ | $215.8344 | $215.8344 |

| 10+ | $213.5136 | $2,135.1360 |

| 100+ | $201.9096 | $20,190.9600 |

| 1000+ | $190.3056 | $95,152.8000 |

| 10000+ | $174.0600 | $174,060.0000 |

| The price is for reference only, please refer to the actual quotation! | ||