Altera Corporation

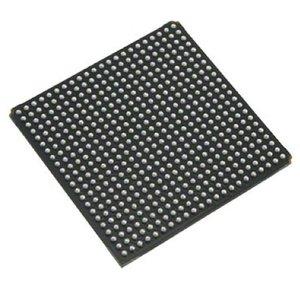

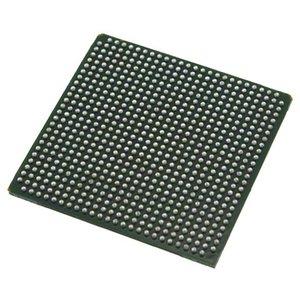

EP1K50FC484

EP1K50FC484 ECAD Model

EP1K50FC484 Attributes

| Type | Description | Select |

|---|---|---|

| Part Life Cycle Code | Obsolete | |

| Supply Voltage-Nom | 2.5 V | |

| Number of Dedicated Inputs | 6 | |

| Number of I/O Lines | 249 | |

| Programmable Logic Type | LOADABLE PLD | |

| Temperature Grade | COMMERCIAL | |

| Package Shape | SQUARE | |

| Organization | 6 DEDICATED INPUTS, 249 I/O | |

| Output Function | REGISTERED | |

| Supply Voltage-Max | 2.625 V | |

| Supply Voltage-Min | 2.375 V | |

| JESD-30 Code | S-PBGA-B484 | |

| Qualification Status | Not Qualified | |

| JESD-609 Code | e1 | |

| Operating Temperature-Max | 70 °C | |

| Number of Terminals | 484 | |

| Package Body Material | PLASTIC/EPOXY | |

| Package Code | BGA | |

| Package Shape | SQUARE | |

| Package Style | GRID ARRAY | |

| Surface Mount | YES | |

| Terminal Finish | TIN SILVER COPPER | |

| Terminal Form | BALL | |

| Terminal Pitch | 1 mm | |

| Terminal Position | BOTTOM | |

| Width | 23 mm | |

| Length | 23 mm | |

| Seated Height-Max | 2.1 mm | |

| Ihs Manufacturer | ALTERA CORP | |

| Reach Compliance Code | unknown | |

| HTS Code | 8542.39.00.01 | |

| Package Description | BGA, | |

| Part Package Code | BGA | |

| Pin Count | 484 | |

| ECCN Code | 3A991.D |

EP1K50FC484 Datasheet Download

EP1K50FC484 Overview

The chip model EP1K50FC484 is a high-performance field-programmable gate array (FPGA) developed by Altera. It is suitable for high-performance digital signal processing, embedded processing, image processing, and other applications. It requires the use of HDL language, such as VHDL, to program the chip.

The EP1K50FC484 chip model has a maximum capacity of 50K logic elements, which can be used to implement complex logic functions and provide a high degree of flexibility. It also features high-speed transceivers, embedded memory blocks, and phase-locked loops (PLLs). This chip model has been used in many applications, such as digital signal processing, embedded processing, image processing, and other tasks that require high-speed and high-performance processing.

The EP1K50FC484 chip model is also suitable for the development and popularization of future intelligent robots. With its high-speed transceivers, embedded memory blocks, and PLLs, it can be used to implement complex logic functions and provide a high degree of flexibility. Additionally, its 50K logic elements can be used to process large amounts of data quickly and accurately. To use the EP1K50FC484 effectively, technical talents such as engineers, software developers, and system architects are needed.

When designing with the EP1K50FC484 chip model, there are several key points to consider. First, the design should be optimized for the specific application. Second, the design should be kept as simple as possible. Third, the design should be made as efficient as possible. Fourth, the design should be tested thoroughly before implementation. Finally, the design should be verified using simulations and other tools.

In conclusion, the EP1K50FC484 chip model is an excellent choice for high-performance digital signal processing, embedded processing, image processing, and other applications. It is also suitable for the development and popularization of future intelligent robots. To use the model effectively, technical talents such as engineers, software developers, and system architects are needed. By following the above key points, the EP1K50FC484 can be used to create efficient and reliable designs.

You May Also Be Interested In

4,567 In Stock

Pricing (USD)

| QTY | Unit Price | Ext Price |

|---|---|---|

| No reference price found. | ||